DMA Model

DMA Approach

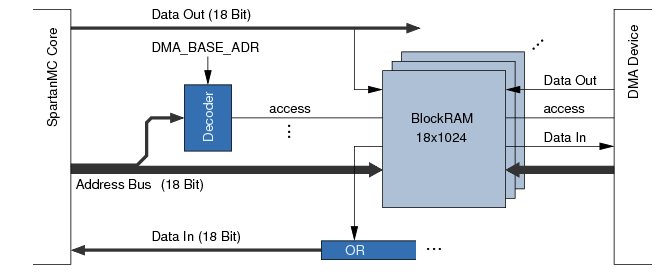

Memory Blocks on FPGAs are generally dual ported. Due to

this fact, we are able to connect one port of the memory

block to the peripheral while the other port is connected

to the SpartanMC address and data bus. The peripheral can

now use the memory to its own liking (even with a different

clock domain).

Schematic of the SpartanMC DMA Model integration

The processor still has arbitrary access to the DMA memory

through data accesses. Typically, this is used for peripherals

which have to work autonomously on large data volumes. Another

possibility is to use that memory as a kind of mailbox system,

where the processor writes commands (leading to action from

the peripheral controller) or reading status information.

Asynchronous activation of the processor is done with an

interrupt signal. Also, the peripheral can monitor the

accesses to the DMA memory to check for new commands, once

the processor changed particular addresses. Alternatively,

the peripheral controller can continuously monitor the

memory cells that hold commands and start working as soon

as a valid change is detected.

It should be mentioned that this concept has two drawbacks:

Firstly, it only works with internal memory of the FPGA.

Secondly, each memory block can only be used by one DMA

capable peripheral. Thus, it is not possible to exchange data

by one DMA capable peripheral to an other without using the

processors core.