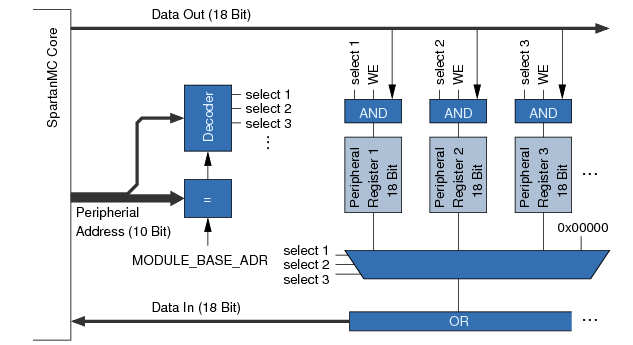

I/O Model

IO Approach

Devices which do not require high bandwidths or don't need

to work autonomously on a large data set can be integrated

via direct connection to the data and address bus of the

SpartanMC. Therefore, the data access in the EX/MEM pipeline

stage uses the computed address to select either the memory

blocks or for a different address region the memory mapped

peripherals.

Each of the peripherals has a select signal as an input and

detects its own subaddress space. Registers in the peripherals

should be synchronized to the processor clock.

The output data (in case of read instructions) of all

peripherals is combined with a distributed multiplexer. Each

of the peripherals produces a zero on its outputs if it is not

accessed. Now all outputs can be combined with a large Or gate

(using the fast carry chains of the FPGA).

Schematic of the SpartanMC IO Model integration

The SpartanMC core provides a dedicated interface for IO

modules. It includes a 10 bit address bus for the peripheral

address space. This peripheral bus is created from the 18 bit

address bus via a core internal address decoder.