Instruction Set

The SpartanMC uses two register addresses per instruction. The

first operand (RD register) is automatically used as the

destination of the operation. The instruction set is composd

of fixed 18 bit instructions grouped in the 4 types shown

below.

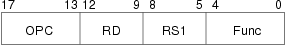

R-Type (Register Instructions) |

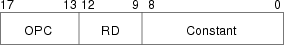

I-Type (Immediate Instructions) |

|

All operation which take two register values and compute a result

which is stored back into operand one.

|

This group includes all operations which take one register value

and a constand to carry out an operation.

|

|

|

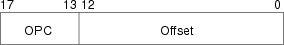

J-Type (Jump Instructions) |

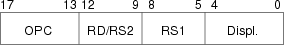

M-Type (Memory Instructions) |

|

This group includes the the jump instruction and two branch

instructions. The branch instructions interprets a conditioncode flag

register to decide either to branch or not

|

This group is used for memory access operations. All load and

store operations are available as half word (9 bit) or full word (18

bit) operation.

|

|

|